## Janki Bhimani Biography:

Dr. Janki Bhimani is an Assistant Professor of Computer Science and Director of the Data Management Research Lab (DaMRL) at Florida International University (FIU). Prior to joining FIU in 2019, she worked with Samsung Semiconductors. She obtained her Ph.D. and M.S. degrees in Computer Engineering from Northeastern University, Boston. Dr. Bhimani's expertise spans the areas of system design, storage systems, memory management, computer architecture, electronic design automation (EDA), cloud computing, big data, modeling and simulation, resource management, capacity planning, machine learning (ML), and high-performance computing (HPC). She is the recipient of the NSF CAREER Award, FIU Top Scholar Award, KFSCIS Excellence in Research Award, Grace Hopper Celebration of Women in Computing (GHC) Faculty Scholarship, and Distinguished Reviewer and Best Paper Awards from flagship conferences. Her research has been supported by \$4.9 million in funding from prestigious federal and state agencies such as NSF and Cyber Florida, as well as industries like Samsung Semiconductors, out of which \$1.8 million are her PI funds. Her research has led to publications in high-impact journals such as IEEE TCC, IEEE TVT, ACM TOS, IEEE TC, ACM TOMACS, IEEE TBDATA, and IEEE TMSCS, and publications in highly selective conferences and workshops such as DAC, HPCA, DATE, CLOUD, HPDC, and HotStorage, earning an h-index of 16 and about 1000 citations, as well as 10 top-graded patent awards. Dr. Bhimani's graduated student alumni have gone on to successful research careers in academia and industry. As an educator, Dr. Bhimani is passionate to demonstrate excellence in her teaching and service roles. She has taught various core and effort intensive graduate and undergraduate level courses such as Storage Systems and Data Structures. She has taken on various leadership roles of general chair, program committee chair, track chair, publicity chair, session chair, etc. in organizing conferences such as CCGRID, ACM HotStorage, and HPDC. Within FIU, she has experience serving on the Faculty Hiring Committee, Awards Committee, CEC Faculty Council, Subject Area Coordinator, Graduate Committee, Diversity, Equity, and Inclusion (DEI) Committee, and Seminar Series Coordinator. Beyond her professional pursuits, in her free time, she is a creative visual artist who paints with oils on canvas.

Further latest details on her work can be found at <a href="https://bhimanijanki.github.io/">https://bhimanijanki.github.io/</a>.

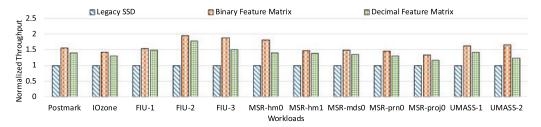

# Janki Bhimani

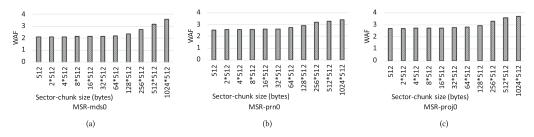

Assistant Professor, Knight Foundation School of Computing and Information Science Florida International University

jbhimani@fiu.edu · Linkedin · Google Scholar · Mobile: +1(857)991-9868 (Please visit my Website for the most updated information.)

#### RESEARCH INTERESTS

System Design, Memory Management; Storage Systems; Computer Architecture; Optimization, Modeling, and Prediction; Resource Management; Cloud Computing; Machine Learning; Capacity Planning; High Performance Storage and Computing; Emerging Non-Volatile Memories;

#### **HIGHLIGHTS**

#### Research:

[Grants.] • Grants: Secured \$4.9 million in research funding from NSF, Cyber Florida, and Samsung Semiconductors with \$1.8 million as PI. Received NSF CAREER award in 2024. Other five proposals under review, including two as PI. Future plans include applying for large grants from DOE, NSF, and AFOSR.

[Awards, Publications, and Patents.] Contributed significantly with 10 high-impact journal articles, 35 peer-reviewed conference papers, 10 patents as lead inventor, and over 900 citations. Recognized with Awards including FIU Top Scholar, KFSCIS Excellence in Applied Research, Distinguished Reviewer, and Best Paper Awards.

[Student Advising/Mentoring.] Graduated one Ph.D. student, who is Assistant Professor, mentored eight Hispanics, one Asian American, and three women in the past five years.

[Collaborations.] Established collaborations with institutions like the University of Maryland, University of Chicago, Argonne National Lab, Syracuse University, and industry leaders Samsung Semiconductors and IBM Research.

#### Teaching:

Designed and taught three core courses, achieving an average student feedback rating of 4.13/5. Secured Quality Matters (QM) certification for courses. Led curriculum update efforts to design and integrate a Data Structures course taught in multiple programming languages. Implemented module-based content distribution with live feedback, and class projects on Chameleon cloud platform.

## Service:

Contributed to FIU's growth, serving on the Faculty Hiring Committee, Awards Committee, CEC Faculty Council, Subject area coordinator, Graduate Committee, DEI Committee, and as Seminar Series Coordinator. Led roles such as General Chair, Publicity Chair for ACM HotStorage, Program Committee Track Chair for CCGRID, and Poster Chair for HPDC. Extensive service as a TPC member for conferences like USENIX FAST, IPDPS, CLOUD. Volunteering at the Center for Women and Gender Studies. Received Grace Hopper Celebration of Women in Computing (GHC) Faculty Scholarship for two years and Certificate of Completion from ASEE DELTA Junior Faculty Institute. Participated in STRIDE workshop for hiring, tenure, and promotion, Diversity Advocate workshop, and Bystander Leadership workshop.

## **EDUCATION**

## Doctor of Philosophy (Ph.D.), Computer Engineering

Aug 2019

Northeastern University, Boston, MA, USA

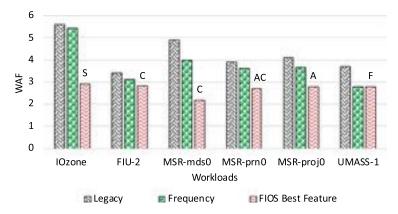

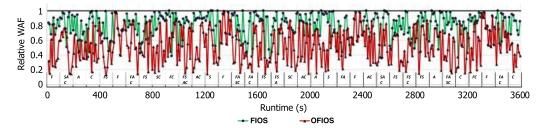

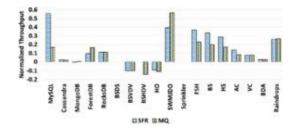

Dissertation: Enhancing Efficiency and Endurance of Flash-Based Storage for Big Data Processing on Enterprise Cloud and Datacenter

## Master of Science (M.S.), Computer Engineering

Jan 2016

Northeastern University, Boston, MA, USA

M.S. research: FiM - Fine grained Model to Predict Heterogeneous Computing Platforms Performance

Bachelor of Technology (B.Tech), Electrical & Electronics Engineering Aug 2013 GITAM University, Vishakhapatnam, India

Major: Robotics and Programming of Embedded Systems, Minor: Circuit Design, Power Management

#### **EXPERIENCE**

## Assistant Professor, Computer Science Aug 2019 - Current Knight Foundation School of Computing and Information Science Florida International University, Miami FL, USA Volunteering Affiliated Faculty Aug 2019 - Current Center for Women's and Gender Studies (CWGS) Florida International University, Miami FL, USA Instructor, College of Engineering Sep 2017 - Dec 2017 Northeastern University, Boston MA, USA **Engineer - Performance Architect** May 2016 - Aug 2018 Samsung Semiconductors Inc. Research Lab, San Jose, CA, USA IC Design Intern Jun 2012 - Jul 2012 Energy Options, Rajkot, India NASA STEM Engagement May 2012 - Jun 2012 NASA's John F. Kennedy Space Center, FL, USA

## PUBLICATIONS IN DISCIPLINE

(\* Indicates an FIU student supervised by myself.)

Citation counts are taken from my Google Scholar Profile, which lists the following statistics: Total citations: 937, h-index: 16, i10-index: 20.

## [Total 45 - 20 FIU (13 with FIU students supervised by myself) and 25 Pre-FIU]

## Selective Refereed Journal Publications

1. Danlin Jia, Li Wang, Natalia Valencia\*, <u>Janki Bhimani</u>, Bo Sheng and Ningfang Mi. Learning-based Dynamic Memory Allocation Schemes for Apache Spark Data Processing. IEEE Transactions on Cloud Computing (TCC) 2023. Tier 1 Journal with impact factor 11.1.

- Ajinkya S Bankar, Shi Sha, <u>Janki Bhimani</u>, Vivek Chaturvedi, Gang Quan. Thermal Aware System-Wide Reliability Optimization for Automotive Distributed Computing Applications. IEEE Transactions on Vehicular Technology (TVT) 2022. Tier 1 Journal with impact factor 2.243.

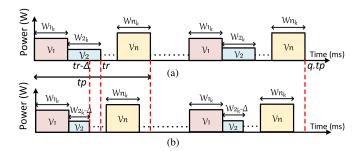

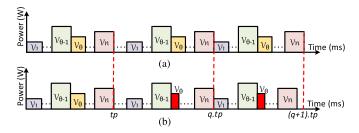

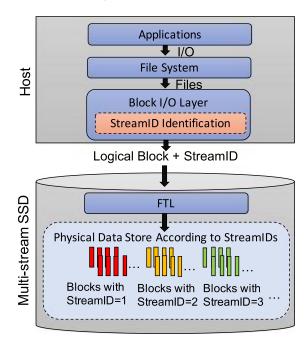

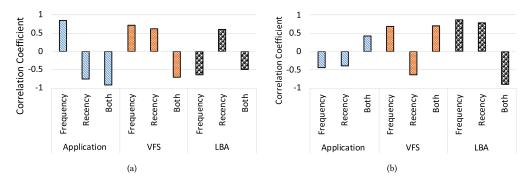

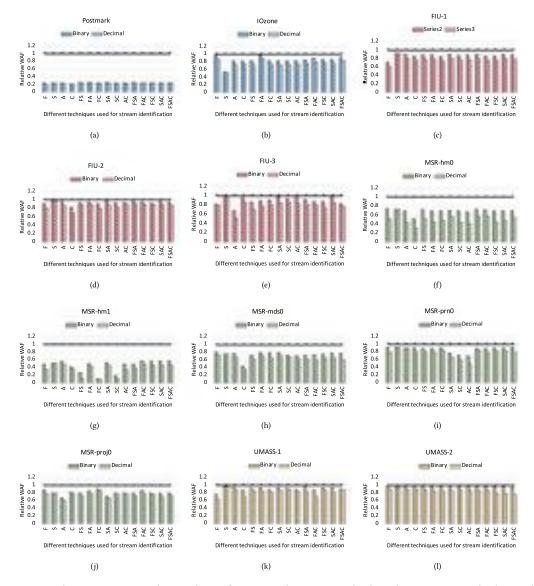

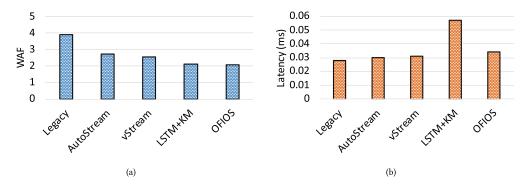

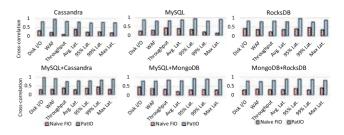

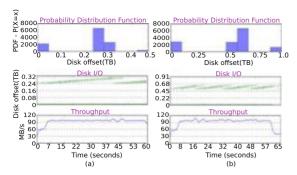

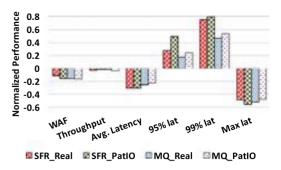

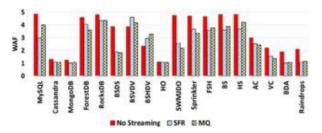

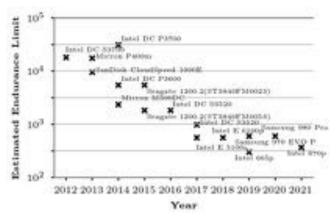

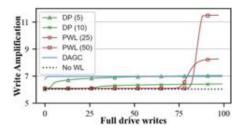

- 3. <u>Janki Bhimani</u>, Zhengyu Yang, Jingpei Yang, Adnan Maruf\*, Ningfang Mi, Rajinikanth Pandurangan, Changho Choi, Vijay Balakrishnan. Automatic Stream Identification to Improve Flash Endurance in Data Centers. ACM Transactions on Storage (TOS) 2021. Tier 1 Journal with impact factor 1.59.

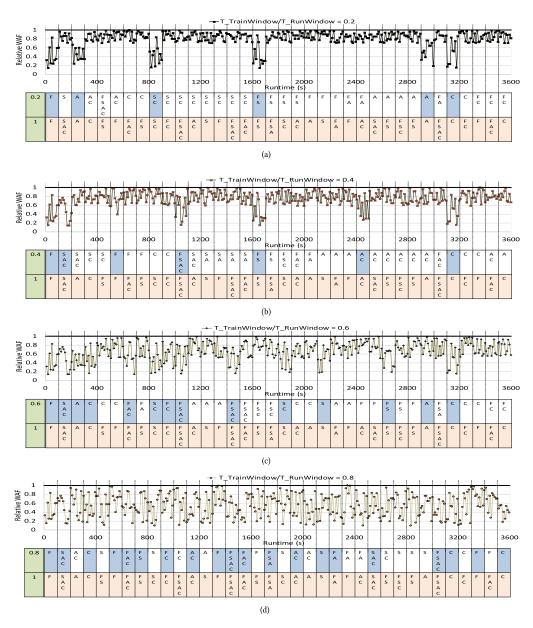

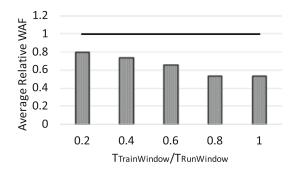

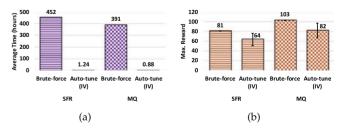

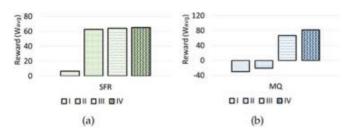

- 4. <u>Janki Bhimani</u>, Adnan Maruf\*, Ningfang Mi, Rajinikanth Pandurangan, and Vijay Balakrishnan. Auto-Tuning Parameters for Emerging Multi-Stream Flash-Based Storage Drives Through New I/O Pattern Generations. IEEE Transactions on Computers (TC) 2020. Tier 1 Journal with impact factor 3.131.

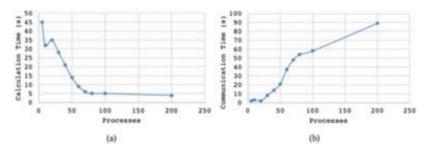

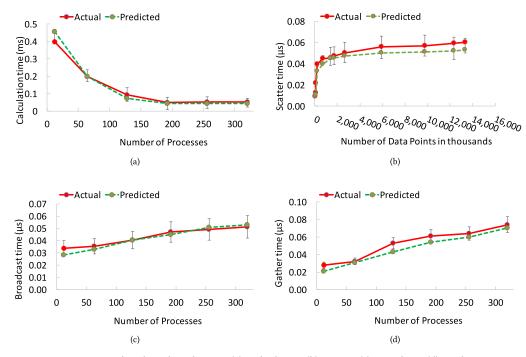

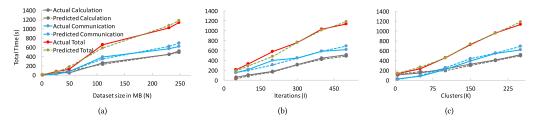

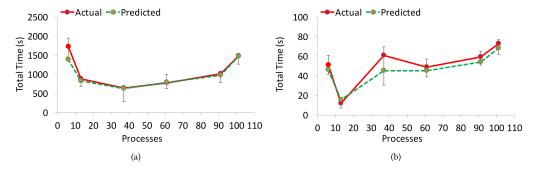

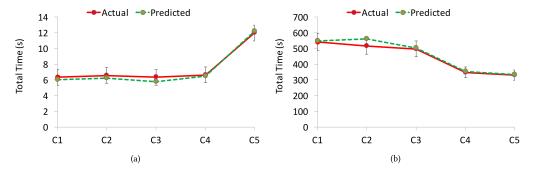

- Janki Bhimani, Ningfang Mi, Miriam Leeser, and Zhengyu Yang, New Performance Modeling Methods for Parallel Data Processing Applications, ACM Transactions on Modeling and Computer Simulation (TOMACS), 2019. DOI 10.1145/3309684. Tier 1 Journal with impact factor 1.380.

- 6. Zhengyu Yang, Manu Awasthi, Mrinmoy Ghosh, <u>Janki Bhimani</u>, and Ningfang Mi, I/O Workload Management for All-Flash Datacenter Storage Systems Based on Total Cost of Ownership, IEEE Transactions on Big Data (TBDATA), Special Issue on the Integration of Extreme Scale Computing and Big Data Management and Analytics, 2018. DOI 10.1109/TBDATA.2018.2871114. Tier 1 Journal with impact factor 2.

- Janki Bhimani, Zhengyu Yang, Ningfang Mi, Jingpei Yang, Qiumin Xu, Manu Awasthi, Rajinikanth Pandurangan, and Vijay Balakrishnan, Docker Container Scheduler for I/O Intensive Applications running on NVMe SSDs, IEEE Transactions on Multi-Scale Computing Systems (TMSCS), 2018. DOI: 10.1109/TMSCS.2018.2801281. Tier 1 Journal with impact factor 2.065.

- 8. Zhengyu Yang, <u>Janki Bhimani</u>, Yi Yao, Cho-Hsien Lin, Jiayin Wang, Ningfang Mi, and Bo Sheng, AutoAdmin: Admission Control in YARN Clusters Based on Dynamic Resource Reservation, Scalable Computing: Practice and Experience, Special Issue on Advances in Emerging Wireless Communications and Networking (SCPE), 2018. Volume 19, Number 1, pp. 53–67.

- 9. Zhengyu Yang, Yufeng Wang, <u>Janki Bhimani</u>, Chiu C. Tan, and Ningfang Mi, EAD: Elasticity Aware Deduplication Manager for Datacenters with Multi-tier Storage Systems, Cluster Computing (CC), 2018. https://doi.org/10.1007/s10586-018-2141-z.

- 10. Zhengyu Yang, <u>Janki Bhimani</u>, Jiayin Wang, David Evans, and Ningfang Mi, Automatic and Scalable Data Replication Manager in Distributed Computation and Storage Infrastructure of Cyber-Physical Systems, Scalable Computing: Practice and Experience, Special Issue on Communication, Computing, and Networking in Cyber-Physical Systems (SCPE), 2018. Volume 18, Number 4, pp. 291–311.

# $\frac{ \mbox{Highly Selective Peer Reviewed Conference Publications}}{\mbox{Acceptance rates below } 30\%}$

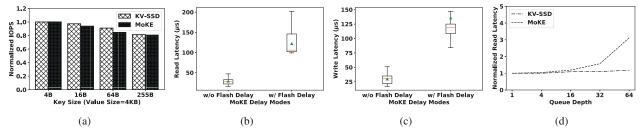

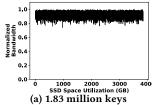

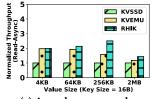

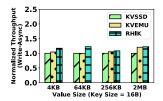

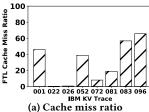

11. Manoj Saha\*, Danlin Jia, <u>Janki Bhimani</u> and Ningfang Mi, MoKE: Modular Key-value Emulator for Realistic Studies on Emerging Storage Devices, 2023 IEEE International

- Conference on Cloud Computing (CLOUD'23), Hybrid Event, Chicago, IL, 2023.

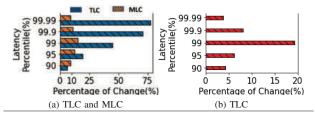

- 12. Ziyang Jiao, Janki Bhimani, Bryan S. Kim, Wear Leveling in SSDs Considered Harmful, 2022 ACM Workshop on Hot Topics in Storage and File Systems (HotStorage '22), Virtual. (Best Paper Award)

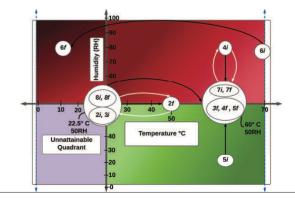

- 13. Adnan Maruf\*, Sashri Brahmakshatriya\*, Baolin Li, Devesh Tiwari, Gang Quan and <u>Janki Bhimani</u>, Do Temperature and Humidity Exposures Hurt or Benefit Your SSDs?, 2022 Design, Automation and Test in Europe Conference. The European Event for Electronic System Design and Test (DATE'22), Virtual. Acceptance Rate: 25%. (Best Paper Award Nomination)

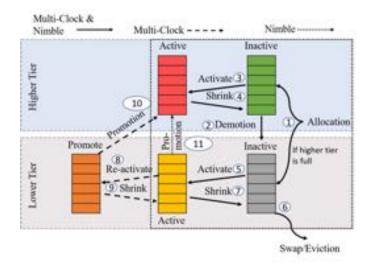

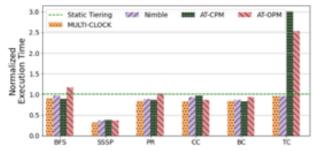

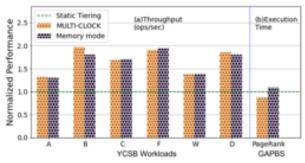

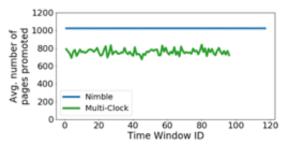

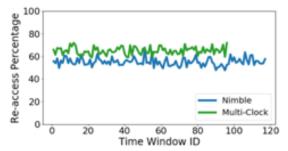

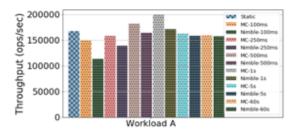

- 14. Adnan Maruf\*, Ashikee Ghosh\*, <u>Janki Bhimani</u>, Daniel Campello, Andy Rudoff, Raju Rangaswami, MULTI-CLOCK: Dynamic Tiering for Hybrid Memory Systems, 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA'22), Seoul, South Korea, 2022. Acceptance Rate: 30%.

- 15. Adnan Maruf\*, Zhengyu Yang, Bridget Davis, Daniel Kim, Jeffrey Wong, Matthew Durand, and <u>Janki Bhimani</u>, Understanding Flash-Based Storage I/O Behavior of Games, 2021 IEEE International Conference on Cloud Computing (CLOUD'21), Online Virtual Congress, 2021. Acceptance Rate: 23.8%.

- 16. <u>Janki Bhimani</u>, Jingpei Yang, Ningfang Mi, Changho Choi, and Manoj Pravakar Saha\*, Fine-grained Control of Concurrency within KV-SSDs, 2021 14th ACM International Systems and Storage Conference (SYSTOR'21), Virtual. Acceptance Rate: 29.9%.

- 17. Manoj Pravakar Saha\*, Bryan Kim, and <u>Janki Bhimani</u>, KV-SSD: What is it Good For?, 2021 Design Automation Conference (DAC'21), San Francisco, CA, 2021. Acceptance Rate: 23%.

- 18. Danlin Jia, Manoj Pravakar Saha\*, <u>Janki Bhimani</u>, and Ningfang Mi, Performance and Consistency Analysis for Distributed Deep Learning Applications, 2020 International Performance Computing and Communications Conference (IPCCC'20), Virtual using Zoom, 2020. Acceptance Rate: 29.3%.

- Janki Bhimani, Rajinikanth Pandurangan, Ningfang Mi, and Vijay Balakrishnan, Emulate Processing of Assorted Database Server Applications on Flash-Based Storage in Datacenter Infrastructures, 2019 International Performance Computing and Communications Conference (IPCCC'19), London, UK, 2019. Acceptance Rate: 29.2%.

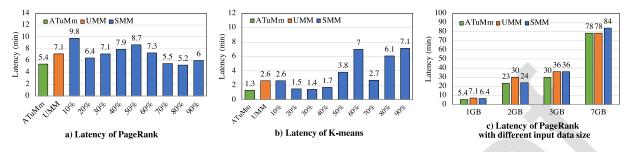

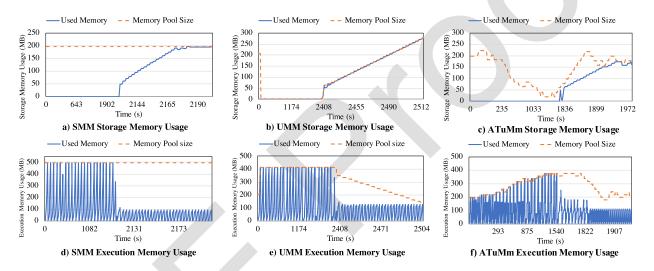

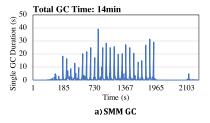

- 20. Danlin Jia, <u>Janki Bhimani</u>, Son Nam Nguyen, Bo Sheng, and Ningfang Mi, ATuMm: Autotuning Memory Manager in Apache Spark, 2019 International Performance Computing and Communications Conference (IPCCC'19), London, UK, 2019. Acceptance Rate: 29.2%.

- Janki Bhimani, Tirthak Patel, Ningfang Mi, and Devesh Tiwari, "What does Vibration do to Your SSD?", 2019 Design Automation Conference (DAC'19), Las Vegas, NV, 2019. Acceptance Rate: 24.3%.

- 22. <u>Janki Bhimani</u>, Ningfang Mi, Zhengyu Yang, Jingpei Yang, Rajinikanth Pandurangan, Changho Choi and Vijay Balakrishnan, "FIOS: Feature Based I/O Stream Identification for Improving Endurance of Multi-Stream SSDs", 2018 IEEE International Conference on Cloud Computing (CLOUD'18), San Francisco, CA, 2018. Acceptance Rate: 15%. (Best Paper Award)

- 23. <u>Janki Bhimani</u>, Ningfang Mi, and Bo Sheng, "BloomStream: Data Temperature Identification for Flash Based Memory Storage Using Bloom Filters", 2018 IEEE International Conference on Cloud Computing (CLOUD'18), San Francisco, CA, 2018. Acceptance Rate: 15%.

- 24. Zhengyu Yang, Morteza Hoseinzadeh, Ping Wong, John Artoux, Clay Mayers, David Thomas Evans, Rory Thomas Bolt, <u>Janki Bhimani</u>, Ningfang Mi, and Steven Swanson, "H-NVMe: A Hybrid Framework of NVMe-based Storage System in Cloud Computing Environment", IEEE International Performance Computing and Communications Conference (IPCCC'17), San Diego, CA, 2017. (Best Paper Award)

- 25. Zhengyu Yang, Morteza Hoseinzadeh, Allen Andrews, Clay Mayers, David Thomas Evans, Rory Thomas Bolt, <u>Janki Bhimani</u>, Ningfang Mi, and Steven Swanson, "AutoTiering: Automatic Data Placement Manager in Multi-Tier All-Flash Datacenter", IEEE International Performance Computing and Communications Conference (IPCCC'17), San Diego, CA, 2017.

- 26. <u>Janki Bhimani</u>, Ningfang Mi, Miriam Leeser, and Zhengyu Yang, "FiM: Performance Prediction Model for Parallel Computation in Iterative Data Processing Applications", IEEE International Conference on Cloud Computing (CLOUD'17), Honolulu, HI, 2017. Acceptance Rate: 18%.

- 27. Han Gao, Zhengyu Yang, <u>Janki Bhimani</u>, Teng Wang, Jiayin Wang, Ningfang Mi, and Bo Sheng, "AutoPath: Harnessing Parallel Execution Paths for Efficient Resource Allocation in Multi-Stage Big Data Frameworks", International Conference on Computer Communications and Networks (ICCCN'17), Vancouver, Canada, 2017. Acceptance Rate: 25%.

- 28. Qiumin Xu, Manu Awasthi, Krishna T. Malladi, <u>Janki Bhimani</u>, Jingpei Yang, and Murali Annavaram. "Performance analysis of containerized applications on local and remote storage" International Conference on Massive Storage Systems and Technology (MSST'17), Santa Clara, CA, 2017.

- 29. <u>Janki Bhimani</u>, Jingpei Yang, Zhengyu Yang, Ningfang Mi, Qiumin Xu, Manu Awasthi, Rajinikanth Pandurangan, and Vijay Balakrishnan, "Understanding Performance of I/O Intensive Containerized Applications for NVMe SSDs", IEEE International Performance Computing and Communications Conference (IPCCC'16), Las Vegas, NV, 2016. Acceptance Rate: 25.50%.

- 30. Zhengyu Yang, Jianzhe Tai, <u>Janki Bhimani</u>, Jiayin Wang, Ningfang Mi, and Bo Sheng, "GREM: Dynamic SSD Resource Allocation in Virtualized Storage Systems with Heterogeneous VMs", IEEE International Performance Computing and Communications Conference (IPCCC'16), Las Vegas, NV, 2016. Acceptance Rate: 25.50%.

# Other Peer Reviewed Conference and Workshop Publications Acceptance rates provided when known

- 31. Manoj P. Saha\*, Omkar Desai, Bryan S. Kim, <u>Janki Bhimani</u>. "Leveraging Keys In Key-Value SSD for Production Workloads" The International ACM Symposium on High-Performance Parallel and Distributed Computing (HPDC'23), Orlando, FL, 2023. (Short Paper)

- 32. Adnan Maruf\*, Daniel Carlson\*, Ashikee Ghosh\*, Manoj Saha\*, <u>Janki Bhimani</u>, Raju Rangaswami. "Allocation Policies Matter for Hybrid Memory Systems" The International

- ACM Symposium on High-Performance Parallel and Distributed Computing (HPDC'23), Orlando, FL, 2023. (Short Paper)

- 33. Manoj P. Saha\*, Bryan S. Kim, Haryadi S. Gunawi, <u>Janki Bhimani</u>. "RHIK Re-configurable Hash-based Indexing for KVSSD" The International ACM Symposium on High-Performance Parallel and Distributed Computing (HPDC'23), Orlando, FL, 2023. (Short Paper)

- 34. Mahsa Bayati, <u>Janki Bhimani</u>, Ronald Lee, Ningfang Mi. "Exploring Benefits of NVMe SSDs for BigData Processing in Enterprise Data Centers" International Conference on Big Data Computing and Communication (BIGCOM'19), Qingdao, China, 2019.

- 35. <u>Janki Bhimani</u>, Jingpei Yang, Zhengyu Yang, Ningfang Mi, NHV Krishna Giri, Rajinikanth Pandurangan, Changho Choi, and Vijay Balakrishnan. "Enhancing SSDs with multistream: What? why? how?" IEEE International Performance Computing and Communications Conference (IPCCC'17), San Diego, CA, 2017. (Short Paper)

- 36. <u>Janki Bhimani</u>, Zhengyu Yang, Miriam Leeser, and Ningfang Mi, "Accelerating Big Data Applications Using Lightweight Virtualization Framework on Enterprise Cloud", IEEE High Performance Extreme Computing Conference (HPEC'17), Waltham, MA, 2017.

- 37. Qiumin Xu, Manu Awasthi, Krishna T. Malladi, <u>Janki Bhimani</u>, Jingpei Yang, Murali Annavaram, "Docker Characterization on High Performance SSDs", IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS'17), Santa Rosa, CA, 2017. (Short Paper)

- 38. Liu Chao, <u>Janki Bhimani</u>, and Miriam Leeser, "Using High Level GPU Tasks to Explore Memory and Communications Options on Heterogeneous Platforms" ACM Workshop on Software Engineering Methods for Parallel and High Performance Applications (SEM4HPC), Washington, D.C., 2017.

- 39. Liu Chao, <u>Janki Bhimani</u>, and Miriam Leeser, "Exploring Memory Options for Data Transfer on Heterogeneous Platforms", The International ACM Symposium on High-Performance Parallel and Distributed Computing (HPDC'17), Washington, D.C., 2017. (Short Paper)

- 40. <u>Janki Bhimani</u>, Miriam Leeser, and Ningfang Mi, "Performance Prediction Techniques for Scalable Large Data Processing in Distributed MPI Systems", IEEE International Performance Computing and Communications Conference (IPCCC'16), Las Vegas, NV, 2016. Acceptance Rate: 12%. (Short Paper)

- 41. <u>Janki Bhimani</u>, Miriam Leeser, and Ningfang Mi, "Design Space Exploration of GPU Accelerated Cluster Systems for Optimal Data Transfer Using PCIe Bus", IEEE High Performance Extreme Computing Conference (HPEC'16), Waltham, MA, 2016.

- 42. <u>Janki Bhimani</u>, Miriam Leeser, and Ningfang Mi, "Accelerating K-Means Clustering with Parallel Implementations and GPU Computing", IEEE High Performance Extreme Computing Conference (HPEC'15), Waltham, MA, 2015.

- 43. <u>Janki Bhimani</u>, Miriam Leeser and Ningfang Mi, "Predicting the Performance of Machine Learning Algorithms running on Heterogeneous Computing Platforms" Women in Machine Learning Workshop (WiML'14), Montréal, Canada, 2014. (Short Paper)

- 44. Baiyu Chen, Zhengyu Yang, Siyu Huang, Xianzhi Du, Zhiwei Cui, <u>Janki Bhimani</u>, Xin Xie, and Ningfang Mi, "Cyber-Physical System Enabled Nearby Traffic Flow Modelling

- for Autonomous Vehicles", IEEE International Performance Computing and Communications Conference, Special Session on Cyber Physical Systems: Security, Computing, and Performance (IPCCC CPS'17), San Diego, CA, 2017.

- 45. Xianfei Xia, Hongru Xiao, Zhengyu Yang, Xin Xie, and <u>Janki Bhimani</u>, Pelletization Characteristics of the Hydrothermal Pretreated Rice Straw with Added Binders. Arabian Journal for Science and Engineering 43, no. 9 (2018): 4811-4820.

Books N/A

Chapters in Books N/A

Government Reports or Monographs N/A

Book Reviews N/A

## PRESENTED PAPERS, AND LECTURES

- 1. Guest Speaker: Picking Research as Career, Women in CS (WiCS) Student Chapter, Miami, FL, April 17, 2023.

- 2. Guest Speaker: Research Towards Data Storage and Management, Presentation Request for Flit-Path Scholars, Miami, FL, February 11, 2022.

- 3. Invited Speaker: Emerging Technologies Moving Forward, Entrepreneurs' Organization (EO), Miami, FL, February 10, 2022.

- 4. Guest Lecture: Towards Designing Intelligent Storage Devices, IBM Research, Almaden, San Jose, CA, May 12, 2021.

- 5. Guest Lecture: Challenges of the Evolving Memory and Storage Technologies, Memory Solutions Lab, Samsung, San Jose, CA, October 23, 2020.

- 6. Guest Speaker: Ph.D. in Computer Science from the lens of a Girl who likes pink, FIU Women in Cybersecurity (WiCys) Student Chapter, Miami, FL, October 22, 2020.

- 7. Guest Lecture: New Techniques for Data Management in Evolving Storage Technologies, Florida International University, Miami, FL, November 22, 2019.

- 8. Guest Lecture: New Storage Technologies for Big Data Processing on Cloud and Datacenter Infrastructures, Colorado State University, Fort Collins, CO, March 27, 2019.

- 9. Paper Presentation Talk: FIOS: Feature Based I/O Stream Identification for Improving Endurance of Multi-Stream SSDs, 2018 IEEE International Conference on Cloud Computing (CLOUD'18), San Francisco, CA, 2018.

- Paper Presentation Talk: BloomStream: Data Temperature Identification for Flash Based Memory Storage Using Bloom Filters, 2018 IEEE International Conference on Cloud Computing (CLOUD'18), San Francisco, CA, 2018.

- 11. Paper Presentation Talk: FiM: Performance Prediction Model for Parallel Computation in Iterative Data Processing Applications, IEEE International Conference on Cloud Computing (CLOUD'17), Honolulu, HI, 2017.

- 12. Paper Presentation Talk: Understanding Performance of I/O Intensive Containerized Applications for NVMe SSDs, IEEE International Performance Computing and Communications Conference (IPCCC'16), Las Vegas, NV, 2016.

- 13. Paper Presentation Talk: Accelerating Big Data Applications Using Lightweight Virtualization Framework on Enterprise Cloud, IEEE High Performance Extreme Computing Conference (HPEC'17), Waltham, MA, 2017.

- 14. Paper Presentation Talk: Design Space Exploration of GPU Accelerated Cluster Systems for Optimal Data Transfer Using PCIe Bus, IEEE High Performance Extreme Computing Conference (HPEC'16), Waltham, MA, 2016.

- 15. Paper Presentation Talk: Accelerating K-Means Clustering with Parallel Implementations and GPU Computing, IEEE High Performance Extreme Computing Conference (HPEC'15), Waltham, MA, 2015.

## CREATIVE WORK

- 1. Conducting a SWOT Analysis as a strategic planning technique has been a key initiative to enhance the overall learning experience of the class.

- 2. Taking the lead in designing and developing the website for the VOCES project, which can be accessed at https://voces.fiu.edu/, has been a significant contribution.

- 3. Creating an efficient workflow that covers the entire lifecycle of multimedia posts, including stages such as concept brainstorming, assignment of responsibilities, post design using tools like Canva, feedback collection and review, post enhancements, and final staging, has streamlined the process.

- 4. Determining the optimal posting frequency and content distribution across various social media platforms, such as LinkedIn, Instagram, and others, with the aim of organically boosting engagement and cultivating student interest in becoming VOCEROs, has been a strategic focus.

- 5. Creating a pioneering teaching method by incorporating surveys and polls to assess student engagement and pinpoint challenging topics has been a transformative approach. Initially breaking down module topics into more digestible sub-topics, prompting students to assess their difficulty through pre-class polls, and then revisiting the sub-topics that most students found challenging in the following class using real-time feedback, employing personalized teaching techniques to enhance understanding, and facilitating an open forum for students to anonymously ask questions has significantly improved the learning experience.

#### WORKS IN PROGRESS

#### **Publications**

- 1. Ali Bin Omer Qureshi\*, Lie Pan, Dheeraj Gandi, Yifan Guo and <u>Janki Bhimani</u>, Optimizing Data Transfers in Edge Computing

- 2. Ali Bin Omer Qureshi\*, Lie Pan, Dheeraj Gandi, Yifan Guo and <u>Janki Bhimani</u>, Data Spilling Reduction in PrestoDB

- 3. Manoj Pravakar Saha\*, Bryan Kim, and Janki Bhimani, Optimizing In-Storage Indexing

- 4. Omkar Desai, Daniel Carlson\*, <u>Janki Bhimani</u>, Bryan S. Kim, Conch: Caching System for Concurrent DNN Training

- 5. Pratik Poudel\*, Jason Liu, <u>Janki Bhimani</u>, Distributed Workload Characterization Optimizer

- 6. Manoj Pravakar Saha\*, Bryan Kim, and <u>Janki Bhimani</u>, DeePaM: Distributed Deep-Learning Page Cache Management for Disaggregated Memory System

- 7. Manoj Pravakar Saha\*, Raju Rangaswami, Yanzhao Wu, and <u>Janki Bhimani</u>, MiPiCheck: Mixed Pipeline Checkpointing

- 8. Manoj Pravakar Saha\*, Ashikee Ghosh\*, Raju Rangaswami, Yanzhao Wu, and <u>Janki Bhimani</u>, LATTICE: Looking Beyond File I/O-based DNN Checkpointing

- 9. Omkar Desai, Adnan Maruf\*, <u>Janki Bhimani</u>, Bryan S. Kim, Modeling the space-time trade-off for the DSI pipeline in ML training.

- 10. Adnan Maruf\*, Ashikee Ghosh\*, <u>Janki Bhimani</u>, and Raju Rangaswami, RUMINANT–Adaptive Tiering for Hybrid Memory Systems.

- 11. Daniel Carlson\*, Adnan Maruf\*, Ashikee Ghosh\*, <u>Janki Bhimani</u>, and Raju Rangaswami, Understanding Hybrid Memory Allocations.

- 12. Adnan Maruf\*, Daniel Carlson\*, <u>Janki Bhimani</u>, Persistent Memory To Better Manage File-backed Pages of Gaming Workloads.

- 13. Adnan Maruf\*, Dwaraka Prasath Mohen Babu\*, Christopher Meadows\*, Ningfang Mi, Bo Sheng, and <u>Janki Bhimani</u>, Data Structure For Low-Overhead Stream Identification.

- 14. Manoj Pravakar Saha\*, Bryan Kim, and <u>Janki Bhimani</u>, Flash Isolation Without Instrumentation Overhead.

- 15. Manoj Pravakar Saha\*, Omkar Desai, Bryan Kim, and <u>Janki Bhimani</u>, Multi-Tenant Key Value Device Indexing.

- 16. Manoj Pravakar Saha\*, Aris Duani Rojas\*, and <u>Janki Bhimani</u>, Parallel Data Access Within Key Value Storage Devices.

#### Proposals Submitted For Review and Under Preparation

## [2 PI + 3 co-PI]

- 1. NSF AI Institute on Neuro-Symbolic AI, under preparation.

- 2. CAHSI-Google Institutional Research Program (IRP): Optimizing Data Workflows in ML, PI, Oct 2024 Sep 2025, \$100,000.

- 3. CSR: Medium: DISCO: Disciplined Data Science Framework for Storage I/O Management, PI, Oct, 2024 Jun 2028, \$1,200,000, My share: \$475,000 (37.5%) PI team: Haryadi S. Gunawi, University of Chicago and Sandeep R. Madireddy, Argonne National Laboratory.

- 4. Samsung GRO: New Techniques for Managing Accelerator Compute and CXL Memory to Improve Performance and Scalability of AI Inference, PI, Oct 2024 - Sep 2026, \$299,852, PI team: Ningfang Mi, Northeastern University.

## FUNDED RESEARCH GRANTS

[9 PI + 3 co-PI/SI = \$4,892,218; Total PI funds = \$1,792,232; My share of PI funds to FIU = \$1,497,303; Co-PI/SI funds to FIU = \$95,750.79]

1. 2024-2029 NSF CAREER (Only PI)

"CAREER-2338457 - Towards Efficient In-storage Indexing"

Total Value: \$615,528 (Direct+Indirect) My share: \$615,528 (100%) Start date: Jul 1, 2024 Expiration date: Jun 30, 2029

## 2. 2024-2026 NSF REU Supplement (Only PI)

"CSR-2406069 - REU: Learning and Management in Tiered Memory Systems"

Total Value: \$16,000 (Direct+Indirect)

Start date: Jan 1, 2024

My share: \$16,000 (100%)

Expiration date: Dec 31, 2024

Project ID: 800020019

## 3. 2023-2026 NSF CISE Core (Only PI)

"CSR-2323100 NSF Core: CSR: Small: Learning and Management in Tiered Memory

Systems"

Total Value: \$514,704 (Direct+Indirect) My share: \$514,704 (100%) Start date: Oct 1, 2023 Expiration date: Sep 30, 2026

Project ID: 800018181

## 4. 2023-2024 Samsung Global Research Outreach (GRO) Award (PI)

"Leveraging Disaggregated Servers for Large Scale AI Training Acceleration"

Co-PI: Bryan Kim, Syracuse University

Total Value: \$50,000 (Direct+Indirect) My share: \$25,000 (50%)

Start date: Sep 1, 2023 Expiration date: Feb 29, 2024

## 5. 2022-2027 NSF HSI (SI)

"HRD-2225201 - HSI Institutional Transformation Project Voces (Voices for Organizing Change in Educational Systems)"

PI team: Yesim Darici, Stephen Secules, Rocio Benabentos, Laird Kramer, Jaroslava

Miksovska, Monica Cardella, FIU

Total Value: \$2,999,986 (Direct+Indirect) My share: \$69,340 (2.3%) Start date: Sep 15, 2022 Expiration date: Aug 31, 2027

#### 6. 2022-2023 Samsung Memory Solutions Lab (MSL) Research Award (PI)

"Leveraging Disaggregated Servers for Large Scale AI Training Acceleration"

Co-PI: Bryan Kim, Syracuse University

Total Value: \$50,000 (Direct+Indirect) My share: \$25,000 (50%)

Start date: Mar 1, 2023 Expiration date: Aug 31, 2023

#### 7. 2021 Samsung Semiconductor Inc. Equipment Grant (Only PI)

"Parallel Data Access with Key-Value SSDs"

Total Value: \$10,000 (Direct+Indirect) My share: \$10,000 (100%) Start date: Oct 1, 2021 Expiration date: Jun 30, 2022

## 8. 2021-2022 NSF REU Supplement (Only PI)

"CNS-2122987 - REU: New Techniques for I/O Behavior Modeling and Persistent Storage

Device Configuration"

Total Value: \$16,000 (Direct+Indirect) My share: \$16,000 (100%) Start date: May 1, 2021 Expiration date: Apr 30, 2022

Project ID: 800014726

## 9. 2020-2023 NSF CISE Core (Lead PI)

"CNS-2008324 - Small: New Techniques for I/O Behavior Modeling and Persistent Storage Device Configuration"

Co-PI: Ningfang Mi, Northeastern University

Total Value: \$500,000 (Direct+Indirect) My share: \$255,071 (51%) Start date: May 1, 2020 Expiration date: Apr 30, 2023

Project ID: 800012359

## 10. 2020-2022 Cyber Florida (Co-PI)

"RumorHunt: A Next-Generation Online Scalable Streaming System"

PI team: Liting Hu, FIU and Zhishan Guo, University of Central Florida Total Value: \$75,000 (Direct+Indirect) My share: \$21,410.79 (28%) Start date: Aug 1, 2020 Expiration date: May 30, 2022

Project ID: 800012574

## 11. 2019-2020 FIU Faculty Grantsmanship Development Program (Co-PI)

"Design, Development and Testing of Distributed Computing Framework for globally coordinated data submission and accessibility of Mass Spectrometry Data"

PI team: Fahad Saeed, Alex Afanasyev, Hadi Amini, FIU

Total Value: \$25,000 (Direct+Indirect) My share: \$5,000 (20%)

Start date: Nov 1, 2019 Expiration date: May 30, 2020

## 12. 2019 Samsung Semiconductor Inc. Equipment Grant (Only PI)

"Exploring Vulnerabilities of Key-Value SSDs"

Total Value: \$20,000 (Direct+Indirect) My share: \$20,000 (100%) Start date: Oct 1, 2019 Expiration date: Sep 30, 2021

#### PROPOSALS SUBMITTED BUT NOT FUNDED

- 1. Pre-Application for ASCR-RENEW (DE-FOA-0002942): Establishing a Sustainable Pathway for Hispanic Students in AI and High-Performance and Scientific Computing Careers at Florida International University (FIU) and Sandia National Laboratories (SNL), Co-PI, PI team: Jason Liu, Raju Rangaswami, Cuong Nguyen, Wenqian Dong, Yanzhao Wu, FIU, Ron Oldfield, Jay Lofstead, Andrew Younge, Patricia Gharagozloo, Sandia National Laboratories (SNL).

- 2. NSF Core: Collaborative Research: CSR: Medium: TensorHeap: Cross-Stack Memory Management for Machine Learning, Co-PI, Aug 2023 Jul 2027, \$546,523, PI team: Raju Rangaswami, Jason Liu, FIU, Ming Zhao, Jia Zou, Arizona State University, and Wujie Wen, Lehigh University.

- 3. NSF CISE Core Medium: LISSA: Learning in the Storage Stack, PI, Jul 2022 Jun 2026, \$1,200,000, PI team: Haryadi S. Gunawi, University of Chicago and Sandeep R. Madireddy, Argonne National Laboratory.

- 4. NSF CAREER: Ameliorate In-storage Indexing, Single PI, Jan 2023 Dec 2028, \$599,789

- 5. DOE CAREER: Techniques to Leverage Emerging Persistent Memories to Accelerate Parallel Data Accesses, Aug 2022 Jul 2027, \$750,000

- 6. NSF CISE: CNS Core: Small: Towards an Adaptive, Multi-Indexed, and Distributed Key-Value Based Flash Storage, PI, Aug 2022 Jul 2025, \$600,000, PI team: Bryan Kim,

- Syracuse University.

- NSF PPoSS large: PPoSS: LARGE: TensorHeap: Cross-Stack Memory Management for Machine Learning, Co-PI, Aug 2022 - Jul 2027, \$2,011,614, PI team: Raju Rangaswami, Jason Liu, FIU, Ming Zhao, Jia Zou, Arizona State University, and Wujie Wen, Lehigh University.

- 8. NSF STC: Science and Technology Center for Decentralized Autonomous Organizations, Key Personnel, Jan 2023 Dec 2028, \$30,000,000, PI team: Yesim Darici, Kemal Akkaya, Hebin Li, Raju Rangaswami, Selcuk Uluagac, Jason Liu, Sukumar Ganapati, Aslihan Akkaya, Laird Kramer, FIU, Ismail Guvenc, North Carolina State University, Ming Zhao, Arizona State University, Shengwang Du, University of Texas at Dallas, Yufei Ding, University of California at Santa Barbara, and Michael Titze, Sandia National Labs.

- NSF Collaborative Research: PPoSS: Planning: Cross-Stack Memory Management for Machine Learning, Co-PI, Aug 2021 - Jul 2023, \$110,000, PI team: Raju Rangaswami, Jason Liu, FIU, Ming Zhao, Jia Zou, Arizona State University, and Wujie Wen, Lehigh University.

- 10. NSF INCLUDES Alliance: Tomorrow's Women in STEM Today (TWIST), Co-PI, Aug 2021 Jul 2026, \$9,257,973, PI team: Yesim Darici, Jessy Abouarab, Mireya Mayor, FIU.

- 11. NSF CAREER: Leveraging Persistent Key-Value SSDs, Single PI, Jan 2021 Dec 2026, \$542,600

- 12. NSF Distributed Infrastructure for Making Mass Spectrometry Data Findable and Accessible, Co-PI, Aug 2021 Sep 2024, \$803,269, PI team: Fahad Saeed and Hadi Amini, FIU.

- 13. NSF NSF INCLUDES: Planning Grant FIU TWIST, Co-PI, Aug 2020 Jul 2022, \$99,998, PI team: Yesim Darici, Jessy Abouarab, Mireya Mayor, FIU.

- 14. NSF CIBR: Distributed Infrastructure for Big Mass Spectrometry Data, Co-PI, Oct 2020

Sep 2023, \$1,048,558, PI team: Fahad Saeed and Hadi Amini, FIU.

- 15. NSF Collaborative Research: PPoSS: Planning: Leveraging Persistent Memory for Trustworthy ML, Co-PI, Aug 2020 Jul 2022, \$146,262, PI team: Raju Rangaswami, FIU, Ming Zhao, Jia Zou, Arizona State University, and Wujie Wen, Lehigh University.

- Facebook Faculty Research Award for Distributed Systems Research: Distributed Systems

for Deep-Learning with Heterogeneous Persistent Storage, Single PI, Aug 2020 Jul 2022,

\$100,000

- 17. Facebook Faculty Research Award for Systems for Machine Learning: System Memory and Storage Management for Deep Learning, Single PI, Aug 2020 Jul 2022, \$100,000

- 18. Microsoft Faculty Award: Efficient Resource Management for Distributed Deep-Learning with Flash-Based Persistent Storage, Single PI, Aug 2020 Jul 2022, \$200,000

- 19. FIU Faculty Grantsmanship Development Program: Visualizing Women's Health in Miami-Dade County, Co-PI, Jan 2019 Dec 2020, \$25,000, PI team: Yesim Darici, Jessy Abouarab.

- 20. FIU Faculty Grantsmanship Development Program: Evaluating Effective Pipeline Strategies for Women in STEM Success Using GIS: What works and what doesn't work in FL Schools, Co-PI, Jan 2020 Dec 2020, \$25,000, PI team: Yesim Darici, Jessy Abouarab.

- 21. Bill & Melinda Gates Foundation: Re-Examining the Patterns of and Motivations for Traditional Contraception Method Use in India and Sub-Saharan Africa: A Mixed-Method Approach, Key Personnel, Aug 2020 Jul 2025, \$1,977,500, PI team: Yesim Darici, Jessy Abouarab, Haiying Long, Sarah Stumbar, Jessica Meadows, Stephany Alvarez-Ventura, FIU and Rahman Tauhidur, Arizona State University.

- 22. NSF CRII: CSR: System Support for Evolving Flash-Based Persistent Storage to Accelerate Parallel Applications, Single PI, May 2020 April 2022, \$174,915.99

## PATENT DISCLOSURES, APPLICATIONS, AND AWARDS

(Content in blue color are items since arriving at FIU.)

Daniel Carlson\*, Adnan Maruf\*, Raju Rangaswami, and <u>Janki Bhimani</u>, inventors; "Techniques to Dynamically Allocate Pages within CXL Memory Systems", Application.

- 2. Manoj Pravakar Saha\*, Yanzhao Wu, Raju Rangaswami, and <u>Janki Bhimani</u>, inventors; "Methods to Efficiently Checkpoint Deep-Learning Model on Persistent Memories", Application.

- 3. Manoj Pravakar Saha\*, Janki Bhimani, inventors; "Flexible and Efficient Data Management Techniques Within Key Value Storage", US 17/340,573.

- 4. Adnan Maruf\*, Ashikee Ghosh\*, Raju Rangaswami, and <u>Janki Bhimani</u>, inventors; "ML based Tiered Memory", US 17/344,449.

- 5. <u>Janki Bhimani</u>, Jingpei Yang, Changho Choi, inventors; Samsung Electronics Co Ltd, assignee. "Parallel key value based multi-thread machine learning exploiting KV-SSDs" US 16/528.492.

- 6. <u>Janki Bhimani</u>, Rajinikanth Pandurangan, Changho Choi, Vijay Balakrishnan, inventors; Samsung Electronics Co Ltd, assignee. "System and method for identifying hot data and stream in a solid-state drive" US 15/895797.

- 7. <u>Janki Bhimani</u>, Rajinikanth Pandurangan, Vijay Balakrishnan, Changho Choi, inventors; Samsung Electronics Co Ltd, assignee. "Methods and systems for testing storage devices via a representative I/O generator" United States patent application US 15/853419.

- 8. <u>Janki Bhimani</u>, Anand Subramanian, Vijay Balakrishnan, and Jingpei Yang, inventors; Samsung Electronics Co Ltd, assignee. "Container workload scheduler and methods of scheduling container workloads" United States patent application US15/820856.

- 9. <u>Janki Bhimani</u>, Jingpei Yang, Changho Choi, Jianjian Huo, inventors; Samsung Electronics Co Ltd, assignee. "Smart I/O stream detection based on multiple attributes" United States patent application US 15/344,422.

- Janki Bhimani, Hingkwan Huen, Jingpei Yang, Manu Awasthi, Vijay Balakrishnan, Jason Martineau, inventors; Samsung Electronics Co Ltd, assignee. "Intelligent controller for containerized applications" United States patent application US 15/379,327.

## PROFESSIONAL ACHIEVEMENTS, HONORS, AWARDS, AND FELLOWSHIPS

- 1. 2024 Received NSF CAREER Award.

- 2. 2023 Received FIU Top Scholar Award in the category of the Research, Creative Activities, and Award-Winning Publications.

- 3. 2023 Quality Matters Certification for Online Course CIS5346 Storage System

- 4. 2022 Received Outstanding Applied Research Award by Knight Foundation School of Computing and Information Science (KFSCIS), FIU.

- 5. 2022 The Best Paper Award at 14th ACM Workshop on Hot Topics in Storage and Filesystem (HotStorage'22).

- 6. 2022 The Best Paper Award Nomination at Design, Automation and Test in Europe Conference. The European Event for Electronic System Design and Test (DATE'22)

- 7. 2022 Quality Matters Certification for Online Course COP3530 Data Structures

- 8. 2021 Awarded Certificate of Completion from ASEE DELTA Junior Faculty Institute

- 9. 2021 Grace Hopper Celebration of Women in Computing (GHC) Faculty Scholarship

- 10. 2021 Recognized as Distinguished Reviewer Award, 13th ACM Workshop on Hot Topics in Storage and File Systems (HotStorage '21)

- 11. 2020 Received Certification for Hybrid Course COP3530 Data Structures

- 12. 2020 Grace Hopper Celebration of Women in Computing (GHC) Faculty Scholarship

- 13. 2019 Outstanding Graduate Research Award, Northeastern University

- 14. 2018 The Best Paper Award at 11th IEEE International Conference on Cloud Computing (IEEE CLOUD)

- 15. 2017 The Best Paper Award at 36th IEEE International Performance Computing and Communications Conference (IPCCC)

- 16. 2014 Double Husky Scholarship, Northeastern University

- 17. 2012 The Best Budget Robot Award at 3rd Lunabotics International Mining Competition, NASA, Kennedy Space Center, FL

- 18. 2012 The Best Working Model Award in Junk Yard Wars at Conscientia, Indian Institute of Space Science Technology (IIST)

- 19. 2012 The Best Paper Award at Aagama National Level Technical Paper Contest

- 20. 2011 The Best Working Model in Junk Yard Wars during Technozion at National Institute Of Technology (NIT)

- 21. 2011 The Outstanding Debate Performance Award by Institute of Engineers India (IEI)

- 22. 2010 The Impromptu Speaker Award by International Society for Technology in Education (ISTE)

- 23. 2010 2013 University Merit Scholarship, GITAM University

## ACADEMIC SUPERVISION

## Doctoral Students (Thesis Advisees)

[10 Ph.D.Thesis Advisees (1 graduated + 1 proposal defended + 3 candidate + 3 discontinued + 2 hired applicant starting next semester), and 10 Ph.D. Committee Member (4 graduated + 3 proposal defended + 3 qualifying passed)]

#### Graduated Ph.D. Students

1. Adnan Maruf, Ph.D. student

Dissertation topic: Improving the performance and reliability of systems with emerging memory and storage devices

Graduated in Apr. 2023

Tenure Track Assistant Professor, Missouri State University

## Current Ph.D. Students (Thesis Advisees)

2. Manoj Pravakar Saha, Ph.D. student

Dissertation topic: Enhancing the in-storage indexing and ML checkpointing

Dissertation plan: Spring 2025

3. Ali Bin Omer Qureshi, Ph.D. student

Dissertation topic: Optimizing Data Spilling in Distributed Query Engine and Memory

Management

Dissertation plan: Fall 2029

4. Mayur Akewar, Ph.D. student

Dissertation topic: Towards Designing New Techniques for AI Based Data Indexing and

Neuro-Symbolic AI

Dissertation plan: Spring 2030

5. Gabriel Rovira, Ph.D. student

Dissertation topic: Improving Data Distribution Pipeline in Heterogeneous Memory Sys-

tem with CXL Devices Dissertation plan: Fall 2030

(2 new Ph.D. students hired starting next semester)

## Discontinued Ph.D. Students

6. Daniel Carlson, Ph.D. student

Dissertation topic: Improving the Performance of Dis-aggregated Memory Systems

Duration advised by me: Fall 2020 - Spring 2024

7. Ashikee Ghosh, Ph.D. student

Dissertation topic: Designing Libraries for Efficient ML Checkpointing

Duration co-advised by me: Spring 2020 - Fall 2023

Software Development Engineer, Amazon

8. Maimuna Begum Kali, Ph.D. student

Dissertation topic: Optimizing Parallel Operations within BigData Processing Platforms Duration advised by me: Fall 2019 - Fall 2021

Ph.D. student, School of Universal Computing, Construction, and Engineering Education (SUCCEED)

## Ph.D. Committee Member

- 9. Rafael Trujillo

- 10. Pratik Poudel

- 11. Pedro Espina

- 12. Sumesh Kumar

- 13. Ziyang Jiao (Syracuse University)

- 14. Omkar Desai (Syracuse University)

- 15. Liana Valdes Rodriguez (Graduated)

- 16. Oswaldo Artiles (Graduated)

- 17. Muhammad Haseeb (Graduated)

- 18. Danlin Jia (Northeastern University) (Graduated)

## M.S. Students (Thesis/Project Advisees)

## [5 M.S. Students (3 graduated + 2 current)]

#### Graduated M.S. Students

- 19. Dwaraka Prasath Mohen Babu, ESpace Networks

- 20. Ashikee Ghosh, Amazon

- 21. Ali Bin Omer Qureshi

## Current M.S. Students

- 22. Shashidhar Reddy Chavula

- 23. Muttahar Khalid

## Research Experience for Undergrad (REU) Students

## Graduated Undergrad Students

- 24. Gabriel Zavala, Dell

- 25. Daniel Carlson

- 26. Roberto Martinez, Co-Founder & CPO of GammaSwap Labs

- 27. Christopher Meadows

- 28. Aris Duani Rojas, Ph.D. Student

- 29. Sashri Brahmakshatriya

- 30. Natalia Valencia, Ph.D. Student

- 31. Kevin Nordman

## Current Undergrad Students

- 32. Federico Monteverdi

- 33. Christopher Lukas Kverne

- 34. Amanda Di Perna

## Independent Study

## [1 M.S. + 3 Undergraduate]

- 1. Daniel Carlson, Summer 2022, Topic: Hybrid Memory Management.

- 2. Dwaraka Prasath Mohen Babu, Spring 2022, Topic: Data Structures to Identify Data Streams.

- 3. Sashri Brahmakshatriya, Summer 2021, Topic: Analyze Reliability of SSDs.

- 4. Christopher Meadows, Summer 2021, Topic: Design Data Stream Identifier.

## Capstone Mentoring

- 1. Daniel Carlson

- 2. Patrick Perez

- 3. Oscar Barbosa

- 4. Nazmul Huq

- 5. Luis Acosta

- 6. Ettore Mottola

- 7. Eitan Flor

- 8. Bryan Camacho

## TEACHING ACTIVITIES

Storage Systems (CIS 5346): The most recent offering of this course was in Fall 2023, and it underwent evaluation by students through the Student Perceptions of Teaching Survey (SPOTs), yielding a commendable mean score of 4.64/5. Notable comments from students include, "The most successful aspect of this course is the detailed information in the lectures about the objectives and executions of each module and great instructor-student interactions." Another student mentioned, "The professor's availability and commitment towards every student was commendable." Additionally, a student highlighted, "This was the best online course that I have taken so far, expertly crafted, and the pacing of this course was good." Lastly, a student appreciated the practicality, stating, "The way we could relate the course to real-life scenarios will definitely help me never forget what I learned. Course material and discussions are thought-provoking and interesting."

Data Structures (COP 3530): COP 3530 earns its "effort-intensive" label due to students' substantial growth expectations post-course and a high enrollment rate. In Fall 2023, my SPOTs rating was 4.19/5. Students praised COP 3530 for being "well-structured," with one noting, "The most successful aspect is probably having discussions for each Module." Another student commended the "Professor's teaching proficiency is 5+ stars rating, she presents lectures in a clear, understandable way with many opportunities in each module to get clarification." The "video lectures" were highlighted for their "easy-to-understand quality." Overall, the course was recognized for its "balance, pacing, and real-world applicability, making it a transformative and great learning experience." The peer evaluation of this course by my colleague Dr. Masoud Milani stated that "my observations, as well as students' opinions, confirm that Dr. Bhimani is an outstanding teacher who has clearly mastered the art of teaching."

## **Graduate Courses Taught**

Overall SPOTS rating: 4.26/5

- 1. CIS 5346: Storage Systems, Fall 2024, Fully-online modality, SPOTs- Number of student: , Response rate: , Overall average: .

- 2. CIS 7980: Ph.D. Dissertation, Summer 2024, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 3. CIS 5346: Storage Systems, Spring 2024, Fully-online modality, SPOTs- Number of student: 34, Response rate: , Overall average: .

- 4. CIS 7980: Ph.D. Dissertation, Spring 2024, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 5. CIS 5346: Storage Systems, Fall 2023, Fully-online modality, SPOTs- Number of student: 15, Response rate: 92.9, Overall average: 4.64/5.

- 6. CIS 7910: Graduate Research, Fall 2023, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 7. CIS 7980: Ph.D. Dissertation, Fall 2023, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 8. CIS 7980: Ph.D. Dissertation, Summer 2023, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 9. CIS 5346: Storage Systems, Spring 2023, Fully-online modality, SPOTs- Number of student: 27, Response rate: 100%, Overall average: 3.8/5.

- 10. CIS 7980: Ph.D. Dissertation, Spring 2023, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 11. CIS 7980: Ph.D. Dissertation, Fall 2022, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 12. CIS 7980: Ph.D. Dissertation, Summer 2022, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 13. CIS 5346: Storage Systems, Spring 2022, Fully-online modality, SPOTs- Number of student: 27, Response rate: 100%, Overall average: 4.11/5.

- 14. CIS 5900: Independent Study, Spring 2022, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 15. CIS 7980: Ph.D. Dissertation, Spring 2022, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 16. CIS 7980: Ph.D. Dissertation, Fall 2021, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 17. CIS 7980: Ph.D. Dissertation, Summer 2021, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 18. CIS 7910: Graduate Research, Spring 2021, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 19. CIS 7980: Ph.D. Dissertation, Fall 2021, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 20. CIS 7910: Graduate Research, Fall 2020, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 21. CIS 7980: Ph.D. Dissertation, Fall 2020, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 22. CIS 7910: Graduate Research, Summer 2020, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 23. CIS 7910: Graduate Research, Spring 2020, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 24. CIS 7980: Ph.D. Dissertation, Spring 2020, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 25. CIS 5346: Storage Systems, Fall 2019, In-person modality, SPOTs- Number of student: 12, Response rate: 75%, Overall average: 4.48/5.

## **Undergraduate Courses Taught**

Overall SPOTS rating: 4.00/5

1. COP 3530: Data Structures, Fully-online modality, Fall 2023, SPOTs- Number of student: 48, Response rate: 83.3, Overall average: 4.19/5.

- 2. COP 3530: Data Structures, Fully-online modality, Spring 2023, SPOTs- Number of student: 60, Response rate: 85.4%, Overall average: 3.64/5.

- 3. COP 3530: Data Structures, Fully-online modality, Fall 2022, SPOTs- Number of student: 47, Response rate: 85.4%, Overall average: 3.93/5.

- 4. CIS 3900 Independent Study, Summer 2022, Hybrid modality, SPOTs- Number of student: 1, Response rate: NA, Overall average: NA.

- 5. COP 3530: Data Structures, Fully-online modality, Spring 2022, SPOTs- Number of student: 39, Response rate: 69.2%, Overall average: 3.85/5.

- 6. COP 3530: Data Structures, Fall 2021, Fully-online modality, SPOTs- Number of student: 47, Response rate: 80.9%, Overall average: 4.2/5.

- 7. CIS 3900 Independent Study, Summer 2021, Hybrid modality, SPOTs- Number of student: 2, Response rate: NA, Overall average: NA.

- 8. COP 3530: Data Structures, Spring 2021, Fully-online modality, SPOTs- Number of student: 51, Response rate: 72.5%, Overall average: 4.43/5.

- 9. COP 3530: Data Structures, Fall 2020, Certified hybrid modality, SPOTs- Number of student: 39, Response rate: 84.6%, Overall average: 2.74/5.

- 10. COP 3530: Data Structures, Spring 2020, Hybrid modality, SPOTs- Number of student: 18, Response rate: 94.4%, Overall average: 4.13/5.

- 11. EECE 2560: Fundamentals of Engineering Algorithms (Northeastern University), Fall 2017, In-person modality, SPOTs- Number of student: 12, Response rate: 80%, Overall average: 4.8/5.

#### OTHER PROFESSIONAL ACTIVITIES AND PUBLIC SERVICE

#### FIU Internal Service

- 1. 2023-2024: KFSCIS Awards Committee

- 2. 2023-2024: CEC Faculty Council Representative

- 3. 2023-2024: KFSCIS Seminar Series Coordinator

- 4. 2023-2024: CEC Faculty representative at United Nations Women and Girls in Science day annual celebrations

- 5. 2023-2024: Graduate Council

- 6. 2022-2023: CEC Faculty Council Representative

- 7. 2022-2023: KFSCIS Seminar Series Coordinator

- 8. 2022-2023: Subject area coordinator: BS-CS for Programming: COP-2210, COP-3337, COP-3530, COP-4238, COP-4226, COP-4520

- 9. 2022-2023: KFSCIS Diversity, Equity & Inclusion (DEI) Committee

- 10. 2022-2023: CEC Faculty representative at United Nations Women and Girls in Science day annual celebrations

- 11. 2022-2023: Graduate Council

- 12. 2021-2022: KFSCIS Tenure Track Faculty Hiring Committee

- 13. 2021-2022: Subject area coordinator: BS-CS for Programming: COP-2210, COP-3337, COP-3530, COP-4338, COP-4226, COP-4520

- 14. 2021-2022: Capstone or Senior Projects Supervisor

- 15. 2021-2022: KFSCIS Diversity Advocate for Faculty Hiring

- 16. 2021-2022: CEC Faculty representative at United Nations Women and Girls in Science day annual celebrations

- 17. 2021-2022: Graduate Council

- 18. 2020-2021: KFSCIS Tenure Track Faculty Hiring Committee

- 19. 2020-2021: Subject area coordinator: BS-CS for Programming: COP-2210, COP-3337, COP-3530, COP-4338, COP-4226, COP-4520

- 20. 2020-2021: Capstone or Senior Projects Supervisor

- 21. 2020-2021: KFSCIS Diversity Advocate for Faculty Hiring

- 22. 2020-2021: KFSCIS Faculty representative at United Nations Women and Girls in Science day annual celebrations

- 23. 2020-2021: Graduate Council

- 24. 2020-2021: KFSCIS Graduate Committee

- 25. 2019-2020: CEC Faculty representative at United Nations Women and Girls in Science day annual celebrations

- 26. 2019-2020: Graduate Council

- 27. 2019-2020: KFSCIS Graduate Committee

#### FIU Microcredential

Remote Teach Ready Badge Summer 2020

#### **Professional Activities**

- 1. General Chair for ACM Workshop on Hot Topics in Storage and File Systems (HotStorage) 2024 leading the overall operations of the workshop.

- 2. TPC for USENIX Conference on File and Storage Technologies (USENIX FAST) 2024 with heavy review workload of 15-20 papers.

- 3. Program Committee Track chair for the track Performance Monitoring, Modeling, Analysis, and Benchmarking (in Cluster, Cloud and Internet Computing) at 22nd IEEE International Symposium on Cluster, Cloud and Internet Computing (CCGrid) 2024.

- 4. Poster chair for the 33nd ACM International Symposium on High-Performance Parallel and Distributed Computing (HPDC) 2024.

- 5. Poster chair for the 32nd ACM International Symposium on High-Performance Parallel and Distributed Computing (HPDC) 2023.

- 6. Publicity chair and TPC for ACM Workshop on Hot Topics in Storage and File Systems (HotStorage) 2023.

- 7. TPC and Session chair for ACM Workshop on Hot Topics in Storage and File Systems (HotStorage) 2022 leading a session on ZNS and SSDs, 2022.

- 8. TPC and Session chair for USENIX Conference on File and Storage Technologies (USENIX FAST) 2021, leading a session on The SSD Revolution Is Not Over.

- 9. TPC and Session chair for ACM Workshop on Hot Topics in Storage and File Systems (HotStorage) 2022 leading a session on Flash Storage, 2022.

- 10. TPC and Session chair for IEEE International Symposium on Workload Characterization (IISWC) 2020, leading a session on System Architecture and Applications.

- 11. TPC for IEEE International Conference on CLOUD Computing, 2022

- 12. TPC for IEEE International Conference on Distributed Computing Systems (ICDCS), Machine Learning on or for Distributed Systems, 2022

- 13. TPC for IEEE/ACM International Symposium on Cluster, Cloud and Internet Computing (CCGrid), Performance Modeling, Scheduling and Analysis Track, 2022

- 14. NSF Panelist for Cyberinfrastructure for Sustained Scientific Innovation (CSSI) program

- 15. TPC for IEEE International Parallel & Distributed Processing Symposium (IPDPS), 2020

- 16. TPC for IEEE International Performance Computing and Communications Conference (IPCCC), 2019, 2020

## Service as Peer Reviewing

#### **Conferences:**

- 1. IEEE International Conference on Distributed Computing Systems (ICDCS)

- 2. IEEE/ACM International Symposium on Cluster, Cloud, and Internet Computing (CC-GRID)

- 3. ACM Workshop on Hot Topics in Storage and File Systems (HotStorage)

- 4. International Symposium on High-Performance Parallel and Distributed Computing (HPDC)

- 5. USENIX Conference on File and Storage Technologies (FAST)

- 6. IEEE International Parallel & Distributed Processing Symposium (IPDPS)

- 7. IEEE International Conference on Cloud Computing (IEEE CLOUD)

- 8. IEEE High Performance Extreme Computing Conference (IEEE HPEC)

- 9. IEEE International Conference on Green Computing and Communications (GreenCom)

- 10. International Conference on Massive Storage Systems and Technology (MSST)

- 11. IEEE International Conference on Big Data (BigData)

- 12. International Conference on Networking, Architecture, and Storage (NAS)

- 13. International Conference on Parallel and Distributed Systems (ICPADS)

- 14. Workshop on Interactions of NVM/Flash with Operating Systems and Workloads (IN-FLOW)

- 15. International Conference on Performance Engineering (ICPE)

- 16. ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)

- 17. IEEE/IFIP International Conference on Dependable Systems and Networks (DNS)

- 18. Big Data and Cloud Performance Workshop at INFOCOM (DCPerf)

- 19. International Conference on Autonomic Computing (ICAC)

- 20. International Conference on Computer Aided Design (ICCAD)

- 21. International Conference on Cloud Computing Technologies and Applications (CloudTech)

- 22. Field-Programmable Custom Computing Machines (FCCM)

- 23. International Conference on Computer. Communication and Networks (ICCCN)

- 24. IEEE International Performance Computing and Communications Conference (IPCCC)

- 25. IEEE/ACM International Conference on Utility and Cloud Computing (UCC)

#### Journals:

- 1. IEEE Transactions on Cloud Computing (TCC), IEEE Journal

- 2. ACM Transaction on Storage (TOS), ACM Journal

- 3. IEEE Transactions on Services Computing (TSC), IEEE Journal

- 4. Simulation Modelling Practice and Theory (SIMPAT), Elsevier Journal

- 5. Computers, MDPI Journal

- 6. Future Generation Computer Systems (FGCS), Elsevier Journal

- 7. IEEE Transactions on Computers (TC), IEEE Journal

- 8. ACM Transactions on Modeling and Performance Evaluation of Computing Systems (TOM-PECS), ACM Journal

## Society Memberships

- 1. Member (2014-present) Association for Computing Machinery (ACM)

- 2. Member (2014-present) Institute of the Electrical and Electronics Engineers (IEEE)

- 3. Member (2014-present) The Advanced Computing Systems Association (USENIX)

## Community Services

1. Volunteering Affiliated Faculty, Center for Women and Gender Studies (CWGS), Florida International University, Miami FL, USA

### PERSONAL TRAITS

Highly motivated and eager to learn new things.

Strong leadership skills and innovative approaches.

Ability to work as an individual as well as in group.

## Research Statement

Janki Bhimani, Assistant Professor,

Knight Foundation School of Computing and Information Science, Florida International University jbhimani@fiu.edu, bhimanijanki@gmail.com · Linkedin · Website · Google Scholar · Mobile: +1(857)991-9868

(Please visit my Website for the most updated information.)

The global datasphere is projected to reach 163 zettabytes by 2025, indicating a profound shift in our daily lives driven by data. As datacenters adapt to meet escalating computational and storage demands, the challenge of efficiently managing this abundance of information becomes critical for system architects. My decade-and-a-half-long research focuses on pioneering simple yet disruptive and efficient solutions for memory management and storage systems to address this challenge. The goal is to establish robust, parallel, and performant computing systems capable of thriving in our data-intensive landscape. This work not only aligns with current federal funding priorities but is imperative for shaping the future, where innovation and efficiency converge to redefine the boundaries of large-scale data-intensive workloads.

[Publication Decisions.] My work as a faculty member primarily focuses on storage systems, system design and architecture, modeling and simulation, and cloud computing domains. Consequently, I have directed my efforts towards the highest-ranked journals in these disciplines, including ACM TOS, IEEE TC, ACM TOMACS, IEEE TCC, and IEEE TVT. For instance, the IEEE Journal of Transactions in Cloud Computing has an impact factor of 11.1, and most of these journals publish less than 10% of submitted manuscripts. Due to the often lengthy time-to-press for journal publications and the time-intensive nature of qualitative research, I frequently target preliminary findings for highly-selective peer-reviewed conferences and workshops such as HPCA, DAC, DATE, HotStorage, CLOUD, and HPDC. This approach enables me to disseminate preliminary findings quickly to target audiences while also building a narrative for subsequent journal publications. Currently, I have 45 peer-reviewed publications, with 20 published after joining FIU in the last five years. I am also the lead inventor of 10 patents. My work has received multiple Best Paper Awards and nominations for the prestigious IEEE MICRO Top Picks Award and In Company of Women Award in the Science and Technology category, showcasing its impact. Additionally, my research is highly cited, with about 1000 citations, an h-index of 16, and an i10-index of 20, reflecting broad influence. Recognizing the excellent quality of my research, I am a recipient of the NSF CAREER Award, FIU Top Scholar Award in the category of Research, Creative Activities, and Award-Winning Publications, and the Outstanding Research Award by the KFSCIS. I have also been invited to speak on my research by various organizations, including the Entrepreneurs' Organization of Miami and industry research labs such as IBM and Samsung Research.

[Research Funding.] In my research, I have achieved significant milestones by securing a total of twelve grants valued at over \$4.9 million, with nine of them valued at over \$1.8 million as the lead/sole Principal Investigator from federal, state, and industry sources such as NSF, Cyber Florida, and Samsung Semiconductors Notably, I am proud of my recent highly competitive NSF CAREER Award towards designing efficient in-storage indexing techniques, and NSF CISE Core small award as the sole PI, focusing on designing new memory management techniques for in-memory analytic frameworks and databases leveraging machine learning (ML). These funding's underscores the significance of my research work in the national discourse. Currently, I am awaiting decisions on five proposals, two of which I lead. Looking forward, my plans involve pursuing grants such as DOE CAREER, NSF Core Medium, and AFOSR to further advance my research.

[Research Collaborations and Advising.] My commitment to advising and mentoring is reflected in the successful graduation of one Ph.D. student who is a tenure-track Assistant Professor at Missouri State University. Over the past five years, I have advised a diverse group, including eight Hispanics, one Asian American, and three Women. Currently, I am supervising a dynamic team comprising six graduate and three undergraduate students and I am in process of hiring two more graduate students starting Fall 2024. Establishing fruitful collaborations is integral to my research approach. I have established partnerships with esteemed institutions such as the University of Maryland, University of Chicago, Argonne National Lab, and Syracuse University, as well as industry leaders like Samsung and IBM Research, contributing to the advancement of our collective research goals.

[Research Experience and Successes.] My research philosophy is centered on advancing "end-to-end system design" to maximize the utilization of available resources and effectively address societal challenges. I am deeply passionate about optimization and emerging technologies. Engaging in interdisciplinary research is a particular interest of mine, and I consider benchmarking and modeling as essential tools for conducting thorough investigations and driving disruptive improvements. At a high level, my research has concentrated on improving two critical components of computer systems: Memory and Storage. Over the last five years as a faculty member, my research contributions can be categorized primarily into the following three directions.

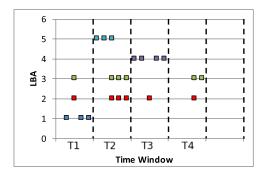

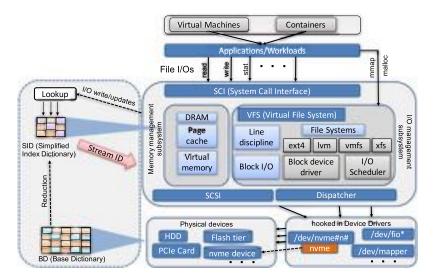

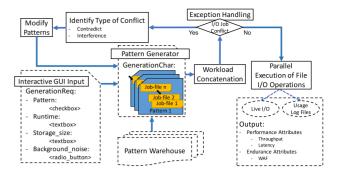

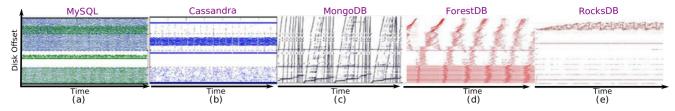

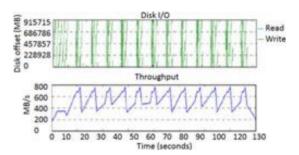

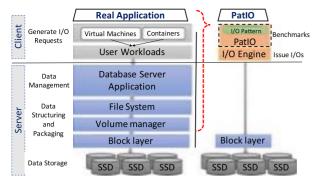

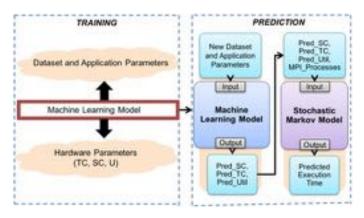

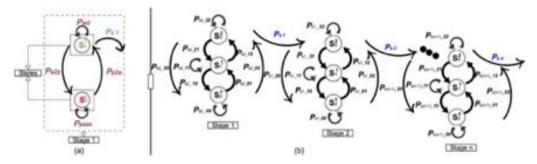

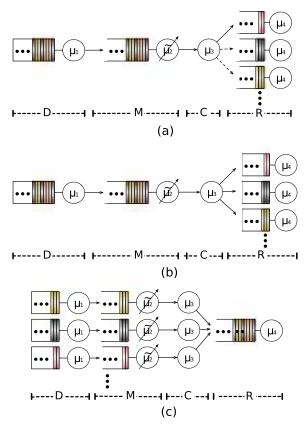

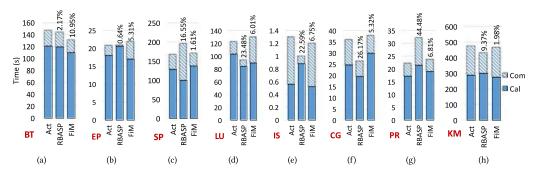

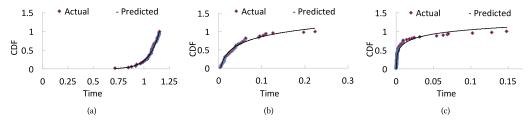

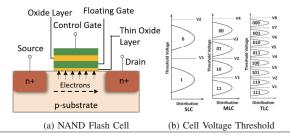

I/O Behavior Modeling, Performance Prediction and Optimization: In the era of "Big Data," where multiple data processing applications coexist in data centers, I/O activities exhibit significant variations. The configuration of existing storage systems, typically done during installation and then permanently maintained, is becoming insufficient. Modern data processing systems present three key challenges. First, simultaneous operations from multiple applications create interference, impacting the performance of solid-state drives (SSDs), unlike hard disk drives (HDDs) with limited bandwidth. Second, while HDD reliability relies on internal mechanical components, SSDs are sensitive to user and

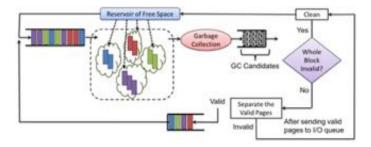

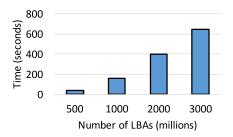

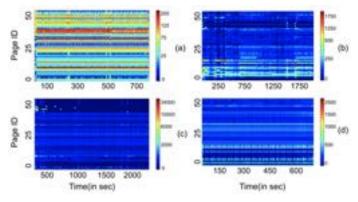

operating system I/O workloads, necessitating optimal configuration for persistent storage. Third, diverse SSD types, including multi-stream SSDs and Key-Value (KV) SSDs, come with distinct internal algorithms and parameters. Selecting and tuning these algorithms based on I/O activities is crucial for optimal performance and flash endurance. Therefore, the research objective is to model the complex I/O activities of diverse applications, dynamically tuning the internal algorithm parameters of flash-based SSDs for optimal performance and reliability.

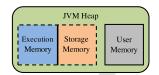

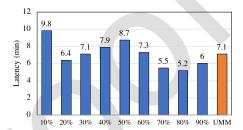

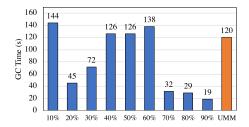

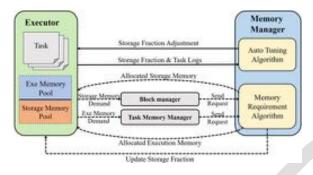

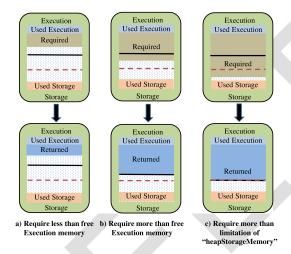

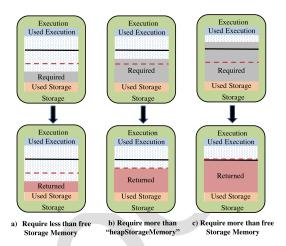

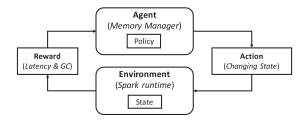

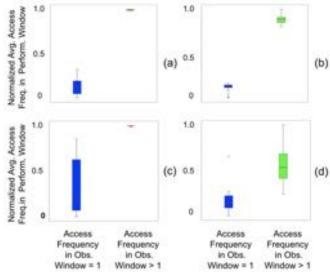

Learning and Management in Tiered Memory Systems: Further, in the past decade, ML has undergone astounding growth, permeating various industries, including storage systems. To tackle the challenges presented by vast amounts of data and optimize memory accesses, tiered memory systems are gaining popularity. These systems employ high-speed memory like DRAM for frequently accessed upper-tier data and slower but larger memories like NVMe NAND flash, 3D-Xpoint, and CXL memories for lower tiers. These systems prove crucial for efficient data management, contributing to improved performance and efficiency, reducing data access times, and lowering overall computing costs. Thus, we design novel tiered memory management techniques, leveraging ML's power and addressing its limits and overheads as a versatile solution to enhance various aspects, including parameter tuning, task scheduling, scanning, migration, and allocation, ultimately optimizing performance, Quality of Service (QoS), and resource utilization in in-memory databases and analytic frameworks.

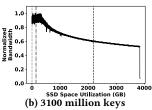

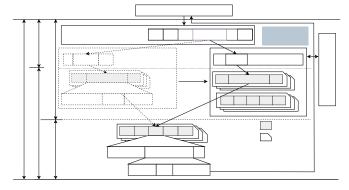

Towards Efficient In-storage Indexing and Device Endurance: In the domain of in-storage indexing, a concept originating in the 1990s, the practical implementation has encountered obstacles, as exemplified by Seagate's 2014 endeavor with Kinetic HDDs, constrained by HDD I/O limitations. However, the prospect of efficient in-storage indexing has recently gained momentum with flash-based SSDs. Early efforts, including our preliminary research, demonstrate that the combination of a fast and lightweight KV database or POSIX-compliant file system with a key-value SSD (KVSSD) performing in-storage indexing outperforms traditional block SSDs. The development of Efficient In-Storage Indexing Devices (ISIDs) poses challenges that necessitate attention to ensure optimal performance and functionality. Firstly, the role of storage device models is pivotal in computer systems research, addressing research gaps related to performance analysis, algorithm development, system evaluation, resource management, and realistic simulations. The lack of a low-cost open-source research platform hampers rapid adoption. Secondly, the design of ISIDs for diverse workloads demands meticulous consideration of indexing techniques, query optimization, data access patterns, and data distribution within the constraints of limited device resources. Therefore, we develop ISID models that capture internal feature dependencies and support dynamic model calibration. This aims to develop new index management techniques efficiently utilizing limited on-device resources while considering flash-specific constraints to optimize endurance and latency for a multi-tenant environment.

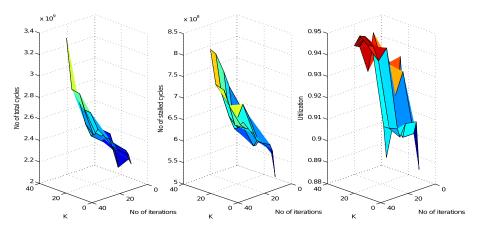

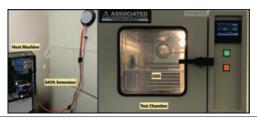

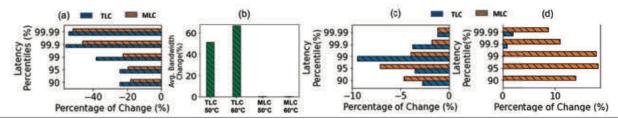

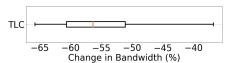

In conjunction with the above, my team has embarked on pursuing various other cutting-edge projects. First, we challenge the assumption that flash-based SSDs are less susceptible to diverse environmental conditions such as vibrations, temperature, and humidity than HDDs. Extensive testing indicates that, even within specified datasheet limits, short-term exposures exhibit lingering effects, and long-term exposure results in over 30% performance degradation. This raises concerns in datacenter performance, affecting tail latency and Service Level Agreements (SLAs) but has even more crucial implications on automotive operating in harsh conditions, with its transition to use more and more complex electronic control systems (ECS) with integrated flash. Leveraging these insights, with a particular focus on the impact of temperature on the reliability of electronic control systems (ECS), we study automotive applications with multi-core processing architectures, taking into account temperature considerations and system-level reliability. We optimize system-wide reliability through a mathematical programming model and a genetic algorithm, accurately predicting system-wide mean-time-to-failure (MTTF) with substantial speed-ups, thereby enhancing reliability analysis.

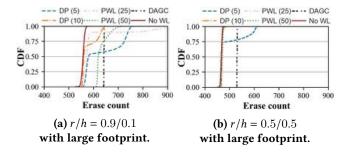

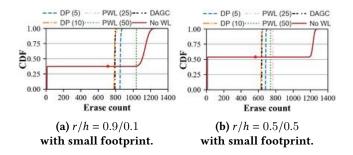

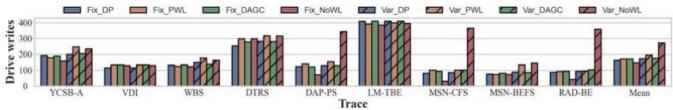

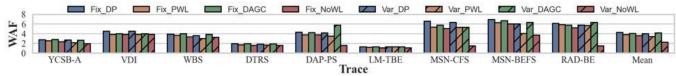

Second, another initiative involves critically examining wear leveling in SSDs, addressing challenges, assessing effectiveness, and advocating for capacity variance. Third, in the space of Systems-for-ML, our team is designing new models to enhance data storage and ingestion pipelines for ML workloads. We are also investigating novel approaches to optimize Deep Neural Network (DNN) checkpointing and versioning beyond traditional file I/O methods and designing models. Forth, in the space of ML-for-Systems, we are leveraging disciplined data science to revolutionize decision-making in storage I/O. Fifth, we are working towards optimizing data spilling in distributed query engine. Lastly, my commitment extends to advocating for positive change in educational systems through the NSF HSI project VOCES - Voices for Organizing Change in Educational Systems, leading efforts in the direction of social media impacts and improving course curriculum. Thus, to conclude, my diverse undertakings showcase my comprehensive engagement in advancing knowledge and addressing pivotal challenges across multiple facets of data storage and computing as well as the education system.

[Future Plan.] In my envisioned trajectory, I am committed to further solidifying my standing as an expert in memory management and storage systems, with a dedicated focus on emerging technologies. My work will continue to contribute to and influence the national discourse around efficient, reliable, and enduring data management techniques. Each successive phase of my research is strategically crafted to make practical and measurable strides towards optimizing data management. My dedication to solving important research problems and consistently publishing in high-quality venues remains unwavering. I plan to enhance my recruitment strategies, aiming to intentionally diversify my doctoral student cohort. Looking forward, I aspire to leverage the national network I have cultivated to foster collaborations on a broader scale. Initiating endeavors for large-scale, multi-institutional funding is a pivotal goal, intended to amplify the impact of my research endeavors and revolutionize data management practices.

# Teaching Statement

Janki Bhimani, Assistant Professor,

Knight Foundation School of Computing and Information Science, Florida International University jbhimani@fiu.edu, bhimanijanki@gmail.com · Linkedin · Website · Google Scholar · Mobile: +1(857)991-9868

(Please visit my Website for the most updated information.)

Designed and taught three core courses, achieving an average student feedback rating of 4.13/5. Secured Quality Matters (QM) certification for all my courses. Led curriculum update efforts to design and integrate a Data Structures course taught in multiple programming languages. Implemented module-based content distribution with live feedback, and class projects on Chameleon cloud platform.

# Teaching Philosophy

As an Assistant Professor, I am thrilled by the opportunity to fully integrate teaching and mentoring into my daily routine. My goal is to motivate students to acquire and apply knowledge, teach them critical thinking skills to solve newly occurring problems in their fields of study, and assist them in building career foundations to succeed after graduation. I emphasize to students that the specifics of all the programming languages, libraries, frameworks, and deployment services that are in vogue at the moment can change at a rapid pace. All new technologies are easy to learn once students have developed strong foundations. Apart from the technical depth of content, I also encourage everyone in the classroom to express their thoughts. To bring technical subjects to life, I teach using a combination of various techniques such as whiteboard discussions, PowerPoint presentations, and audio-visual illustrations, such as a demo of sorting algorithms using UNO cards. A sample of my demonstrative lecture can be found here.

I believe that students learn more by thinking than by memorizing. Therefore, before delving into any new topic, I explain the key challenges and questions that initially motivated its exploration and how various ideas evolved over time to nurture problem-solving capabilities. For example, in this lecture on solid-state drives, I first explain why students should learn about the topic, highlighting its exciting advantages and key challenges that motivated various branches of different research works.

In the growing and ever-changing field of computer science and engineering, I view teaching not only as the transmission of knowledge to students but also as a means of inspiring independent inquiry and learning. It is a collaborative process that fosters improvement for both students and me. To illustrate how I embody these principles in my lectures, consider this lecture on NAND cells within SSDs. As students gain insights into the complexities of NAND cells, I, too, gain a deeper understanding through the process of explanation, fostering a continuous cycle of learning and teaching in the ever-changing landscape of computer science and engineering. Recognizing the uniqueness of each student, I have learned and will continue to tailor my mentoring style to bring out the best in every individual.

# Teaching Experience

At FIU I have designed two courses from scratch and taught multiple semesters of graduate and undergraduate courses in different modalities, including in-person, certified hybrid, and certified synchronous and asynchronous online formats. The courses I taught include Storage Systems and Data Structures, Independent Study, Senior Project, and Capstone Project. For all my courses, I have developed module-based content that provides the necessary scaffolding to span the space for better understanding of the concepts learned. With input from peers at the Center for the Advancement of Teaching (CAT), colleagues within our department, teaching assistants, and student feedback, I have taken several measures to enhance the teaching process. These include developing a precursor covering basic concepts before the start of the course, creating a mechanism to incorporate student feedback during the same semester, and crafting a well-structured syllabus with course-level objectives. Additionally, I have outlined module-level objectives and explained their alignment with course-level objectives, improved course content, and designed clear rubrics for all assignments, making it easier for students to understand expectations. Next, I elaborate the content of some of my courses, highlighting my favorite parts.

Storage Systems (CIS 5346): Teaching the advanced graduate-level Storage Systems course has been a stimulating academic pursuit. This course delves into a diverse array of topics, encompassing the introduction to storage systems, storage devices (Hard Disk Drives, Solid State Drives), storage system components, storage architecture, large-scale distributed storage systems, datacenter storage, non-volatile memory (NVM), reliability and fault tolerance (RAID Systems), performance, file-systems, operating systems storage management, memory and storage concepts (Caching, Consistency, and Deduplication), disks and scheduling, and emerging storage technologies and future trends.